Introduction

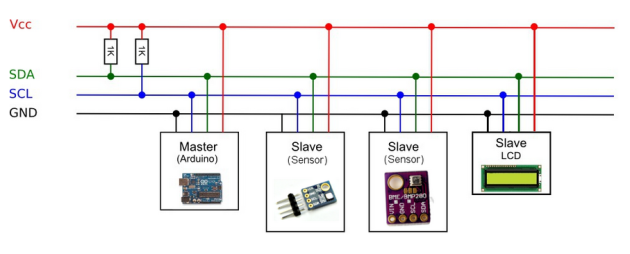

Dans le cadre de petite installation peu coûteuse, la technologie I2C est souvent employée, rappels :

Un abonné prend le contrôle du bus I²C en émettant une condition de départ : Niveau haut sur SCL & Front descendant sur SDA ; cet abonné devient le maître.

Après avoir pris le contrôle, le maître transmet un octet contenant l'adresse de l'esclave (sur 7 bits) ainsi que l'opération effectuée : Lecture = NL 1 ; Ecriture = NL 0.

Lorsque l'esclave a détecté son adresse, il émet un bit d'acquittement (ACK) au niveau logique bas.

Le maître envoie des données à l'esclave. A la fin de la transmission de chaque octet, l'esclave émet un acquittement.

L'esclave envoie des données au maître. A la fin de la transmission d'un octet, le maître émet un acquittement s'il veut recevoir encore un octet ou bien un non acquittement (NL 1) s'il a terminé de recevoir.

Pour terminer la communication, le maître émet une condition d'arrêt : Niveau haut sur SCL & Front montant sur SDA.

Ci-joint le fichier de l'activité dirigé au format pdf.

Ci-joint le fichier de l'activité dirigé au format odt.